# Atmel

#### Atmel AVR 8-bit Microcontroller

## AVR151: Setup and Use of the SPI

#### **APPLICATION NOTE**

## Introduction

This application note describes how to set up and use the on-chip Serial Peripheral Interface (SPI) of the Atmel<sup>®</sup> AVR<sup>®</sup> microcontroller. Most AVR devices come with an on board SPI and can be configured according to this document. This document contains, theoretical background and the steps to configure the SPI to run in both master mode and slave mode.

#### **Features**

- SPI Pin Functionality

- Multi Slave Systems

- SPI Timing

- SPI Transmission Conflicts

- Emulating the SPI

- Code examples for Polled operation

- Code examples for Interrupt Controlled operation

## **Table of Contents**

| Int | oduc                                                    | tion                                        | 1  |  |

|-----|---------------------------------------------------------|---------------------------------------------|----|--|

| Fe  | atures                                                  | 5                                           | 1  |  |

| 1.  | Gene                                                    | eral Description of the SPI                 | 3  |  |

|     | 1.1.                                                    | Data Transmission Between Master and Slave  | 3  |  |

|     | 1.2.                                                    | Pins of the SPI                             | 4  |  |

|     | 1.3.                                                    | Multi Slave Systems - SS Pin Functionality  | 4  |  |

|     | 1.4.                                                    | SPI Timing                                  | 6  |  |

|     | 1.5.                                                    | Considerations For High Speed Transmissions | 8  |  |

|     | 1.6.                                                    | SPI Transmission Conflicts                  | 9  |  |

| 2.  | Setu                                                    | Setup the SPI1                              |    |  |

| 3.  | Example 1: SPI Communication Controlled by Polling      |                                             |    |  |

|     | 3.1.                                                    | Master Side                                 | 11 |  |

|     | 3.2.                                                    | Slave Side                                  |    |  |

| 4.  | Example 2: SPI Communication Controlled by Interrupts13 |                                             |    |  |

|     | 4.1.                                                    | Master Side                                 |    |  |

|     | 4.2.                                                    | Slave Side                                  |    |  |

| 5.  | Conclusion15                                            |                                             |    |  |

| 6.  | Revision History                                        |                                             |    |  |

## 1. General Description of the SPI

The SPI allows high-speed synchronous data transfer between the AVR and peripheral devices or between several AVR devices. On most parts the SPI has a second purpose where it is used for In System Programming (ISP). Refer to the AVR910 application note for details.

The interconnection between two SPI devices always happens between a master device and a slave device. Compared to some peripheral devices like sensors, which can only run in slave mode, the SPI of the AVR can be configured for both master and slave mode. The mode the AVR is running in is specified by the settings of the master bit (MSTR) in the SPI control register (SPCR). Special considerations about the  $\overline{SS}$  pin have to be taken into account. This is described in Multi Slave Systems - SS Pin Functionality on page 4.

The master is the active part in this system and has to provide the clock signal a serial data transmission is based on. The slave is not capable of generating the clock signal and thus can not get active on its own. The slave just sends and receives data, if the master generates the necessary clock signal. The master, however, generates the clock signal only while sending data. That means the master has to send data to the slave to read data from the slave.

## 1.1. Data Transmission Between Master and Slave

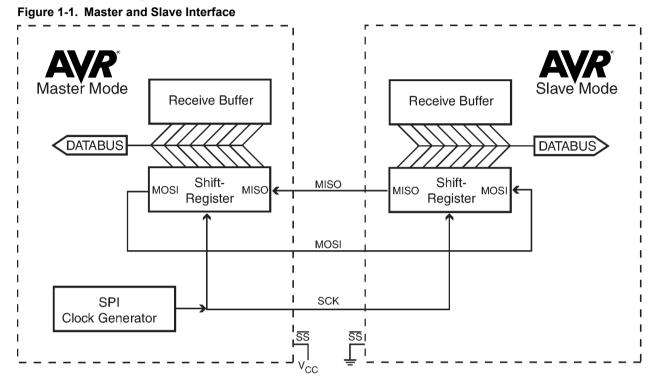

The interaction between a master and a slave AVR is shown in Figure 1-1 Master and Slave Interface on page 3. Two identical SPI units are displayed. The left unit is configured as master while the right unit is configured as slave. The MISO, MOSI, and SCK lines are connected with the corresponding lines of the other part. The mode in which a part is running determines if they are input or output signal lines. Because a bit is shifted from the master to the slave and from the slave to the master simultaneously in one clock cycle both 8-bit shift registers can be considered as one 16-bit circular shift register. This means that after eight SCK clock pulses the data between master and slave will be exchanged.

The system is single buffered in the transmit direction and double buffered in the receive direction. This influences the data handling in the following ways:

- 1. New bytes to be sent cannot be written to the data register (SPDR) / shift register before the entire shift cycle is completed.

- 2. Received bytes are written to the Receive Buffer immediately after the transmission is completed.

- 3. The Receive Buffer has to be read before the next transmission is completed or data will be lost.

- 4. Reading the SPDR will return the data of the Receive Buffer.

After a transfer is completed the SPI Interrupt Flag (SPIF) will be set in the SPI Status Register (SPSR). This will cause the corresponding interrupt to be executed if this interrupt and the global interrupts are enabled. Setting the SPI Interrupt Enable (SPIE) bit in the SPCR enables the interrupt of the SPI while setting the I bit in the SREG enables the global interrupts.

#### 1.2. Pins of the SPI

The SPI consists of four different signal lines. These lines are the shift clock (SCK), the Master Out Slave In line (MOSI), the Master In Slave Out line (MISO) and the active low Slave Select line ( $\overline{SS}$ ). When the SPI is enabled, the data direction of the MOSI, MISO, SCK, and  $\overline{SS}$  pins are overridden according to the following table.

#### Table 1-1. SPI Pin Overrides

| Pin  | Direction Master Mode | Direction Slave Mode |

|------|-----------------------|----------------------|

| MOSI | User Defined          | Input                |

| MISO | Input                 | User Defined         |

| SCK  | User Defined          | Input                |

| SS   | User Defined          | Input                |

This table shows that the input pins are automatically configured. The output pins must be initialized manually by the software. The reason for this is to avoid damages through driver contention.

#### 1.3. Multi Slave Systems - SS Pin Functionality

The Slave Select ( $\overline{SS}$ ) pin plays a central role in the SPI configuration. Depending on the mode the part is running in and the configuration of this pin, it can be used to activate or deactivate the devices. The  $\overline{SS}$  pin can be compared with a chip select pin which has some extra features.

In master mode, the  $\overline{SS}$  pin must be held high to ensure master SPI operation if this pin is configured as an input pin. A low level will switch the SPI into slave mode and the hardware of the SPI will perform the following actions:

- 1. The master bit (MSTR) in the SPI Control Register (SPCR) is cleared and the SPI system becomes a slave. The direction of the pins will be switched according to Table 1-2 Overview of the SS Pin Functionality on page 5.

- 2. The SPI Interrupt Flag (SPIF) in the SPI Status Register (SPSR) will be set. If the SPI interrupt and the global interrupts are enabled the interrupt routine will be executed.

This can be useful in systems with more than one master to avoid two masters accessing the SPI bus at the same time. If the  $\overline{SS}$  pin is configured as output pin it can be used as a general purpose output pin which does not affect the SPI system.

**Note:** In cases where the AVR is configured for master mode and it can not be ensured that the  $\overline{SS}$  pin will stay high between two transmissions, the status of the MSTR bit has to be checked before a new byte is written. After the MSTR bit has been cleared by a low level on the  $\overline{SS}$  line, it must be set by the application to re-enable SPI master mode.

In slave mode the  $\overline{SS}$  pin is always an input. When  $\overline{SS}$  is held low, the SPI is activated and MISO becomes output if configured so by the user. All other pins are inputs. When  $\overline{SS}$  is driven high, all pins are inputs, and the SPI is passive, which means that it will not receive incoming data. The following table shows an overview of the  $\overline{SS}$  Pin Functionality.

| Mode   | SS Configuration | SS Pin-level | Description                                |

|--------|------------------|--------------|--------------------------------------------|

| Slave  | Always Input     | High         | Slave deactivated (deselected)             |

|        |                  | Low          | Slave activated (selected)                 |

| Master | Input            | High         | Master activated (selected)                |

|        |                  | Low          | Master deactivated, switched to slave mode |

|        | Output           | High         | Master activated (selected)                |

|        |                  | Low          |                                            |

Table 1-2. Overview of the  $\overline{SS}$  Pin Functionality

**Note:** In slave mode, the SPI logic will be reset once the  $\overline{SS}$  pin is brought high. If the  $\overline{SS}$  pin is brought high during a transmission, the SPI will stop sending and receiving immediately and both data received and data sent must be considered as lost.

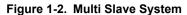

As shown in the preceding table , the  $\overline{SS}$  pin in slave mode is always an input pin. A low level activates the SPI of the device while a high level causes its deactivation. A Single Master Multiple Slave System with an AVR configured in master mode and  $\overline{SS}$  configured as output pin is shown in the following figure. The amount of slaves which can be connected to this AVR is only limited by the number of I/O pins to generate the slave select signals.

The ability to connect several devices to the same SPI-bus is based on the fact that only one master and only one slave is active at the same time. The MISO, MOSI, and SCK lines of all the other slaves are tristated (configured as input pins of a high impedance with no pullup resistors enabled). A false implementation (e.g. if two slaves are activated at the same time) can cause a driver contention which can lead to a CMOS latchup state and must be avoided. Resistances of 1 to  $10k\Omega$  in series with the pins of the SPI can be used to prevent the system from latching up. However this affects the maximum usable data rate, depending on the loading capacitance on the SPI pins.

Unidirectional SPI devices require just the clock line and one of the data lines. The device can use MISO line or the MOSI line depending on its purpose.

## 1.4. SPI Timing

The SPI has four modes of operation, 0 through 3. These modes essentially control the way data is clocked in or out of an SPI device. The configuration is done by two bits in the SPI control register (SPCR). The clock polarity is specified by the CPOL control bit, which selects an active high or active low clock. The clock phase (CPHA) control bit selects one of the two fundamentally different transfer formats. To ensure a proper communication between master and slave both devices have to run in the same mode. This might require a reconfiguration of the master to match the requirements of different peripheral slaves.

The settings of CPOL and CPHA that specify the different SPI modes are shown in the following table.

| Table 1-3. | SPI Mode  | Configuration |

|------------|-----------|---------------|

|            | 011110000 | ooningaration |

| SPI mode | CPOL | СРНА | Shift SCK-Edge | Capture SCK-<br>Edge |

|----------|------|------|----------------|----------------------|

| 0        | 0    | 0    | Falling        | Rising               |

| 1        | 0    | 1    | Rising         | Falling              |

| 2        | 1    | 0    | Rising         | Falling              |

| 3        | 1    | 1    | Falling        | Rising               |

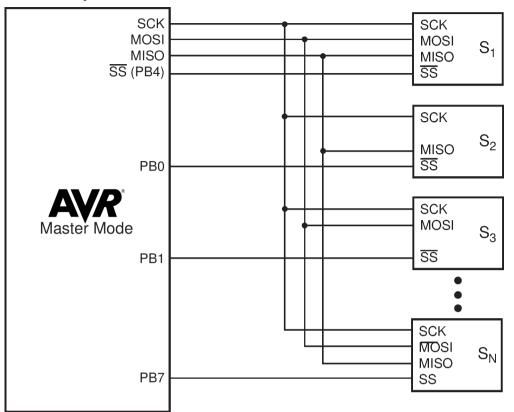

The clock polarity has no significant effect on the transfer format. Switching this bit causes the clock signal to be inverted (active high becomes active low and idle low becomes idle high). The settings of the clock phase, however, selects one of the two different transfer timings. Since the MOSI and MISO lines of the master and the slave are directly connected to each other, the diagrams show the timing of both devices, master and slave. The  $\overline{SS}$  line is the slave select input of the slave. The  $\overline{SS}$  pin of the master is not shown in the diagrams. It has to be inactive by a high level on this pin (if configured as input pin) or by configuring it as an output pin.

#### 1.4.1. CPHA = 0 and CPOL = 0 (Mode 0) And CPHA = 0 And CPOL = 1 (Mode 1)

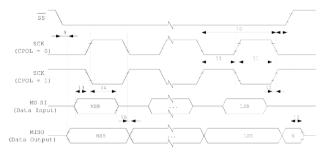

The timing of a SPI transfer where CPHA is zero is shown in the following figure. Two wave forms are shown for the SCK signal - one for CPOL equals zero and another for CPOL equals one.

#### Figure 1-3. SPI Transfer Format with CPHA = 0

\*Not defined but normally MSB of character just received.

When the SPI is configured as a slave, the transmission starts with the falling edge of the SS line. This activates the SPI of the slave and the MSB of the byte stored in its data register (SPDR) is output on the MISO line. The actual transfer is started by a software write to the SPDR of the master. This causes the clock signal to be generated. In cases where the CPHA equals zero, the SCK signal remains zero for the first half of the first SCK cycle. This ensures that the data is stable on the input lines of both the master and the slave. The data on the input lines is read with the edge of the SCK line from its inactive to its active state (rising edge if CPOL equals zero and falling edge if CPOL equals one). The edge of the SCK line from its inactive state (falling edge if CPOL equals zero and rising edge if CPOL equals one) causes the data to be shifted one bit further so that the next bit is output on the MOSI and MISO lines.

After eight clock pulses the transmission is completed. In both the master and the slave device the SPI interrupt flag (SPIF) is set and the received byte is transferred to the receive buffer.

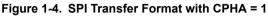

#### 1.4.2. CPHA = 1 and CPOL = 0 (Mode 2) And CPHA = 1 And CPOL = 1 (Mode 3)

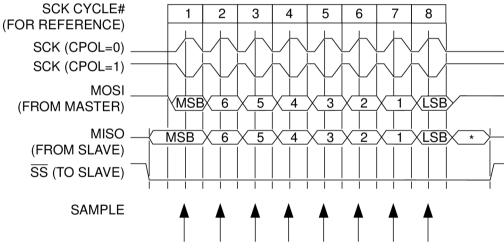

The timing of a SPI transfer where CPHA is one is shown in the following figure. Two wave forms are shown for the SCK signal - one for CPOL equals zero and another for CPOL equals one.

\*Not defined but normally LSB of previously transmitted character.

Like in the previous cases the falling edge of the  $\overline{SS}$  lines selects and activates the slave. Compared to the previous cases, where CPHA equals zero, the transmission is not started and the MSB is not output by the slave at this stage.

The actual transfer is started by a software write to the SPDR of the master what causes the clock signal to be generated. The first edge of the SCK signal from its inactive to its active state (rising edge if CPOL equals zero and falling edge if CPOL equals one) causes both the master and the slave to output the MSB of the byte in the SPDR. As shown in the preceding figure there is no delay of half a SCK-cycle like in Mode 0 and 1. The SCK line changes its level immediately at the beginning of the first SCK-cycle. The data on the input lines is read with the edge of the SCK line from its active to its inactive state (falling edge if CPOL equals zero and rising edge if CPOL equals one).

After eight clock pulses the transmission is completed, in both the master and the slave device the SPI interrupt flag (SPIF) is set and the received byte is transferred to the receive buffer.

## 1.5. Considerations For High Speed Transmissions

Parts which run at higher system clock frequencies and SPI modules capable of running at speed grades up to half the system clock require a more specific timing to match the needs of both the sender and receiver. The following two diagrams show the timing of the AVR in master and in slave mode for the SPI Modes 0 and 1. The exact values of the displayed times vary between the different parts and are not an issue in this application note. However, the functionality of all parts is in principle the same so that the following considerations apply to all parts.

The minimum timing of the clock signal is given by the times "1" and "2". The value "1" specifies the SCK period while the value "2" specifies the high / low times of the clock signal. The maximum rise and fall time of the SCK signal is specified by the time "3". These are the first timings of the AVR to check if they match the requirements of the slave.

The Setup time "4" and Hold time "5" are important times because they specify the requirements the AVR has on the interface of the slave. These times determine how long before the clock edge the slave has to have valid output data ready and how long after the clock edge this data has to be valid.

The time "6" (Out to SCK) specifies the minimum time the AVR has valid output data ready before the clock edge occurs. This time can be compared to the Setup time "4" of the slave.

The time "7" (SCK to Out) specifies the maximum time after which the AVR outputs the next data bit while the time "8" (SCK to Out high) the minimum time specifies during which the last data bit is valid on the MOSI line after the SCK was set back to its idle state.

#### Figure 1-6. Timing Slave Mode

In principle, the timings are the same in slave mode like previously described in master mode. Because of the switching of the roles between master and slave the requirements on the timing are inverted as well. The minimum times of the master mode are now maximum times and vice versa.

#### 1.6. SPI Transmission Conflicts

A write collision occurs if the SPDR is written while a transfer is in progress. Since this register is just single buffered in the transmit direction, writing to SPDR causes data to be written directly into the SPI shift register. Because this write operation would corrupt the data of the current transfer, a write-collision error in generated by setting the WCOL bit in the SPSR. The write operation will not be executed in this case and the transfer continues undisturbed.

A write collision is generally a slave error, because a slave has no control over when a master will initiate a transfer. A master - however, knows when a transfer is in progress. Thus, a master should not generate write collision errors, although the SPI logic can detect these errors in a master as well as in a slave mode.

## 2. Setup the SPI

The configuration of the SPI in master mode will be shown in two different ways. The first example will show how to implement an SPI communication which is controlled by polling the interrupt flags. The second example will show how to implement an interrupt controlled communication.

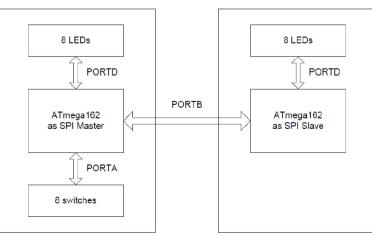

A communication between two AVR devices is shown by sending a text string from the part configured as master to the other part configured as slave. The received character is compared with the expected one (transmitted character) and the result of this communication test is output on the Port D in slave. These examples are well suited to be implement by using two development boards like the STK<sup>®</sup>600.

In all the examples shown here the SPI is configured to run in mode 0 with MSB transmitted first. This is done by setting the bits CPOL, CPHA and DORD in the register SPCR to zero. In the same register the SPI is enabled by setting the SPE bit, while the SCK frequency is specified to CK/4 in the first example. It is set to CK/16 in the second example.

To compare the configuration of the SPI in the different examples the attention has to be directed on the settings of the Master / Slave Select (MSTR) bit and the SPI Interrupt Enable (SPIE) bit. **Note:**

- 1. Because both examples show the transmission between a single master and a single slave it is not necessary to check if the MSTR bit is still set before the master initiates a new transmission. This code has to be added in a multi master application.

- Although the settings of the Clock Rate Select bits have no effect in slave mode it has to be ensured that the system clock (CK) of the slave is at least four times higher than the SPI clock (SCK).

- 3. Pending SPI interrupts are cleared by a dummy access to the SPSR and the SPDR.

Both the master and the slave projects developed in Atmel Studio 7 are available along with this application note.

To run the code, setup two STK600 development boards as shown in the following figure. The MISO, MOSI and SCK lines of both master and slave are connected together. The SS of slave should be connected to the ground. Ensure that both the STK600 boards are connected to common ground. The code is written for ATmega162, but can be compiled for any part with hardware SPI and PORTA, PORTB and PORTD. In this application, when any one of the switches connected to the master is pressed the SPI transmission is initiated.

#### Figure 2-1. Hardware Setup

# Atmel

## 3. Example 1: SPI Communication Controlled by Polling

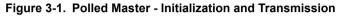

#### 3.1. Master Side

If no interrupts are used, then there is just the SPI module and its pins to be configured. Important in this example is the setting of the  $\overline{SS}$  pin as output pin. This has to be done before the SPI is enabled in master mode. Enabling the SPI while the  $\overline{SS}$  pin is still configured as an input pin would cause the SPI to switch to slave mode immediately if a low level is applied to this pin. This pin is always configured as an input pin in slave mode. Using polling gives the fastest communication. This is why polling is most commonly used in master mode.

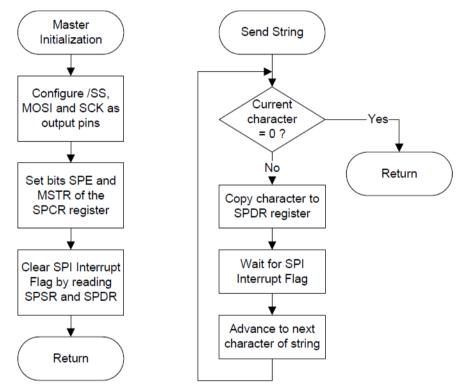

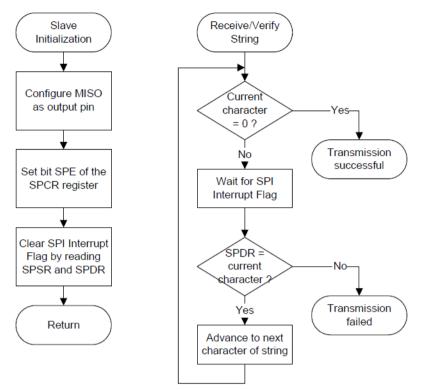

#### 3.2. Slave Side

To configure the AVR to run in slave mode, there is no order in which the registers must be initialized. The MISO pin has to be defined as an output pin, while all other pins are configured automatically as input pins if the SPI is enabled. To configure the AVR to run in slave mode the MSTR bit has to be set to zero. In this case, the Clock Rate Select bits SPR0 and SPR1 do not care because of the synchronous transmission.

All other settings of the SPI configuration register (SPCR) have to be the same as in master mode. This is essential for a successful communication between the two devices.

## 4. Example 2: SPI Communication Controlled by Interrupts

In master mode, interrupt controlled communication makes mainly sense if the SCK clock is generated by dividing the system clock by a large division factor (like 64 or 128). In this case the processor can perform other processes instead of just waiting to send/receive the next byte. In slave mode, where the part does not know when a communication starts, an interrupt controlled implementation can ensure that the part will react in time so that write collision errors will be avoided.

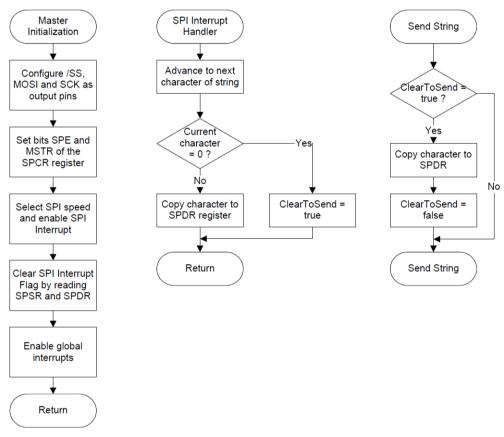

### 4.1. Master Side

The initialization of the SPI happens similar to the previous example. Similar to the master mode, the SS pin has to be set as output first and then the SPI can be enabled. The SPI interrupt is enabled by setting the SPIE bit in the SPCR.

#### Figure 4-1. Interrupt Controlled Master - Initialization and Transmission

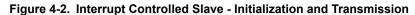

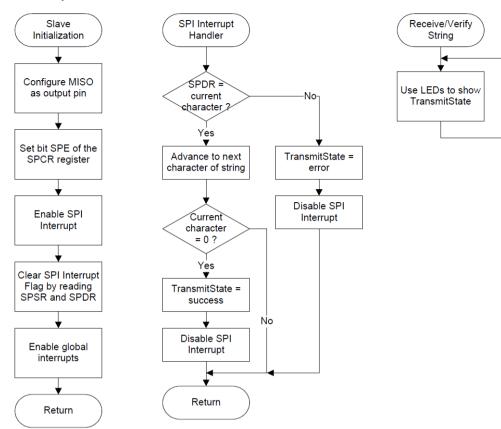

#### 4.2. Slave Side

A slave never knows when the master is going to start a new communication. Interrupts are a perfect feature to react on such undetermined events. So this is a common way to implement the SPI in slave mode.

In this example the main program has to be notified about transmission errors and the completion of the transmission.

## 5. Conclusion

This application note has illustrated the basic SPI communication. When the SPI transmission is successful i.e. when the data received at the slave matches the actual data transmitted by the master via SPI bus, the value of '0xAA' is written to PORD register. When the SPI transmission fails, the value of '0xF0' is written to the PORTD register. This can be visually verified on STK600 with the help of onboard LEDs.

# 6. Revision History

| Doc. Rev. | Date    | Comments                                                                                                            |

|-----------|---------|---------------------------------------------------------------------------------------------------------------------|

| 2585D     | 02/2016 | Updated the firmware to the latest version of Atmel Studio (Atmel Studio 7) and made minor changes in the document. |

| 2585C     | 07/2008 |                                                                                                                     |

| 2585B     | 2006    |                                                                                                                     |

| 2582A     | 2006    | Initial document release.                                                                                           |

# Atmel Enabling Unlimited Possibilities

🗗 🗹 in 8 🖸 W

I

**Atmel Corporation**

1600 Technology Drive, San Jose, CA 95110 USA

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2016 Atmel Corporation. / Rev.: Atmel-2585D-Setup-and-Use-of-the-SPI\_AVR151\_Application Note-02/2016

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, AVR<sup>®</sup>, STK<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as military-grade.